概述

阅读本文章前请确认对X86下的分页机制有最基本的了解,否则将难以理解本文中提到的内容。

本文介绍的内容均位X86架构下的PAE技术,而不是ARM架构下的LPAE技术,虽然两者从本质来说是一样的。

介绍下列内容:

- PAE 技术因何问世

- PAE 技术可以干什么

- PAE 技术实现原理

- 为什么我们所用的 32 位操作系统只能使用 4GB 的内存

PAE 技术因何问世

PAE(Physical Address Extension,中文译名:物理地址扩展)技术最初是为了弥补32位地址在服务上不够用的情况。因为32位的地址最多只能支持4GB的内存,而这对于很多服务器来说是远远不够的,而那时64位的CPU和操作系统还没有普及,这个技术临时缓解了一下这类问题。

PAE 技术可以干什么

PAE技术可以使得多个进程使用的总内存大于 4GB,但是单个进程的所使用的内存上限依然只有 4GB。

PAE 技术实现原理

- 地址线由 32 根增加到 36 根,寻址空间自然也就从 4GB 增加到了 64GB。

- 改动了分页机构使其可以适应36根地址线的寻址空间。

本文主要介绍分页机构的改动。

未启动 PAE 下的分页机制

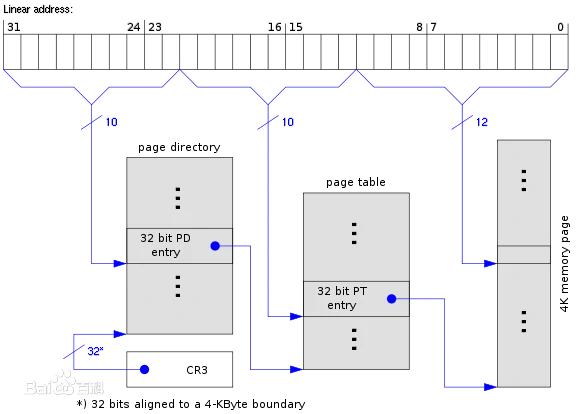

4K 分页

- 从 CR3 寄存器中取出页目录的基址。

- 取出线性地址中的 22 位~31 位共 10 位作为页目录项在页目录中的索引,由此找到页目录项。

- 根据页目录项中的内中找到对应的页表的基址。

- 取出线性地址中的 12 位~21 位共 10 位作为页表项在页表中的索引,由此找到页表项。

- 取出线性地址中的 0 位~11 位共 12 位作为页内偏移,从页表项中取出页基址,两者相加则到物理地址。

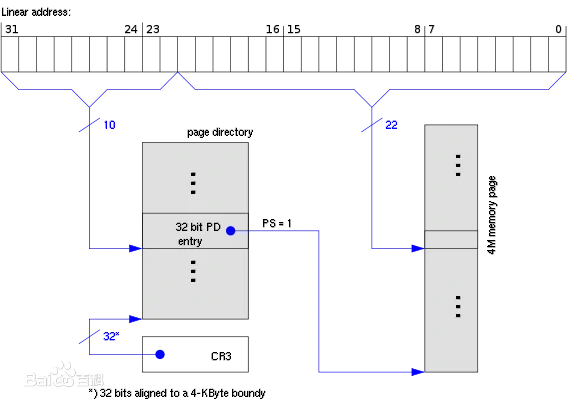

4M分页

- 从 CR3 寄存器中取出页表的基址。

- 取出线性地址中的 22 位~31 位共 10 位作为页表项在页表中的索引,由此找到页表项。

- 取出线性地址中的 0 位~21 位共 22 位作为页内偏移,从页表项中取出页基址,两者相加则到物理地址。

启动 PAE 下的分页机制

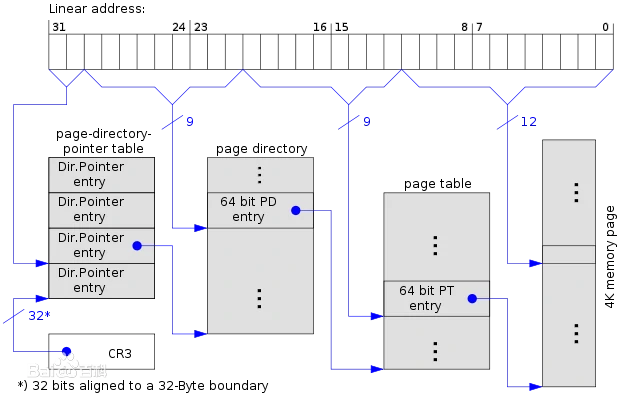

<>4K 分页

- 从 CR3 寄存器中取出页目录指针表的基址。

- 取出线性地址的 30 位~31 位共 2 位作为页目录指针在页目录指针表中的索引,由此找到页目录指针。

- 根据页目录指针获得对应的页目录的基址

- 取出线性地址中的 21 位~29 位共 9 位作为页目录项在页目录中的索引,由此找到页目录项。

- 根据页目录项找到对应页表的基址。

- 取出线性地址中的 12 位~20 位共 9 位作为页表项在页表中索引,由此找到页表项。

- 取出线性地址中的 0 位~11 位共 12 位作为页内偏移,从页表项中取出页基址,两者相加则到物理地址。

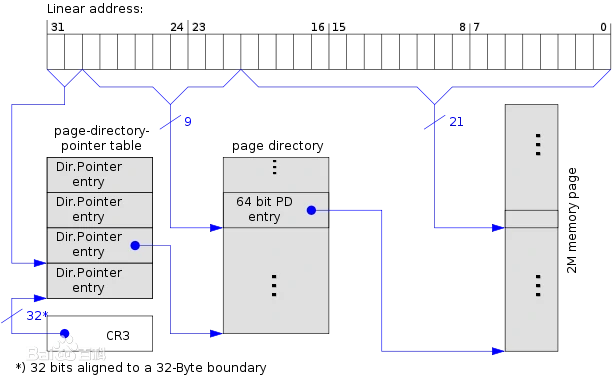

4M 分页

- 从 CR3 寄存器中取出页表指针表的基址。

- 取出线性地址的 30 位~ 31 位共 2 位作为页表指针在页表指针表中的索引,由此找到页表指针。

- 根据页表指针找到对应的页表的基址。

- 取出线性地址中的 21 位~29 位共 9 位作为页表项在页表中的索引,由此找到页表项。

- 取出线性地址中的 0 位~21 位共 22 位作为页内偏移,从页表项中取出页基址,两者相加则到物理地址。